I could not get the 32K dynamic RAM card to work properly. It worked, but not at all reliably. There were many read errors, so bad that it was impossible to run even a short program from RAM.

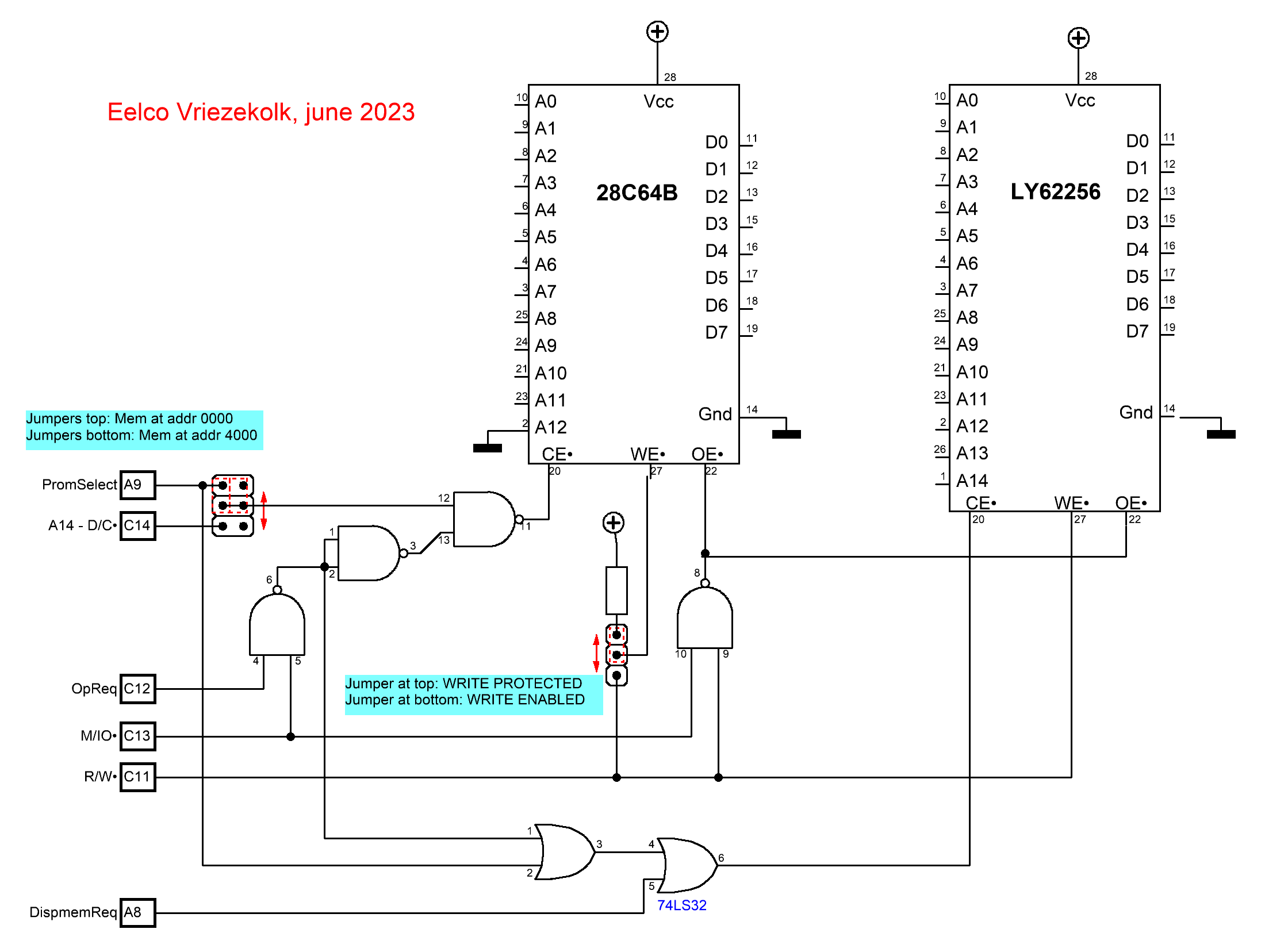

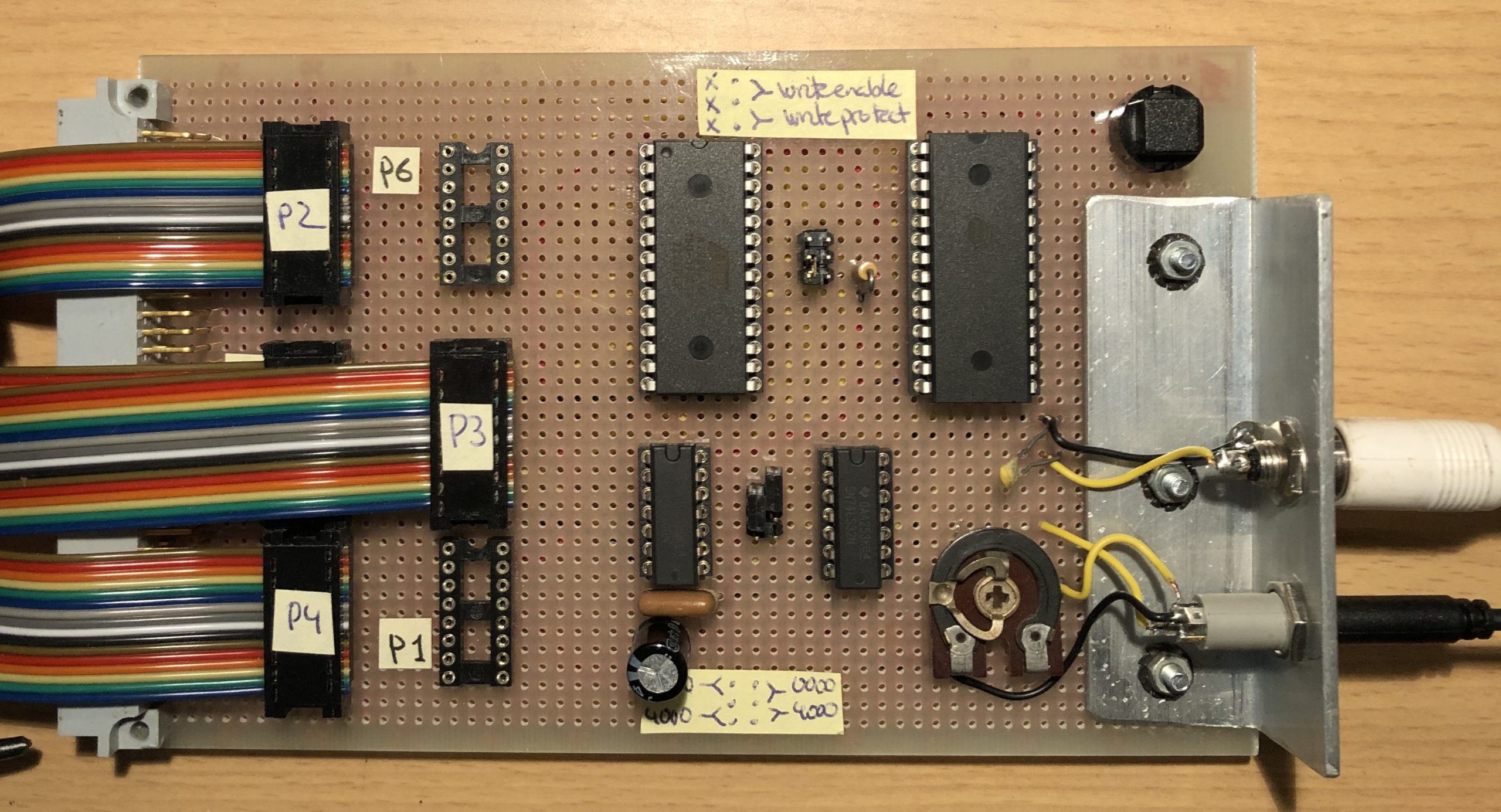

After lots of fruitless debugging, I decided to leave it for the moment. There is a modern chip that contains 32K of statis RAM, with a pin-out that very closely resembles that of the ROM-replacement that I already added. The chip is a LY62256 (full documentation). The circuit and a photo of the resulting board are shown below.

The new circuit appeared to work, but had the same unreliable read-errors as the 32K dynamic RAM board. This means that the fault is not with the board, but somewhere else. After thoroughly cleaning the board and reseating all ICs the problem appears to be gone. I will try the 32K dynamic RAM card at a later time.

The daughterboard with the ROM was changed to the circuit below. Again, the connectors on the left refer to the P1 bus. Only a 74LS32 is necessary for the control signals. Signals marked with a bullet • are active-low; normally active-low is indicated by an overline, but that is cumbersome in sPlan.

On the right you can see the LY62256 and the 74LS32.

I used this program to exercise and test the memory. It steps through memory in blocks of 256 bytes at a time, displaying a spinner. Each block is set to ‘5A’, and then read to verify that it really contains ‘5A’. If not, the offending memory location, expected value and actual value are displayed and the next block is tried. If the test passes, it is repeated with values ‘A5′, ’00’ and ‘FF’. After all blocks from Startp to Endp have been tested, a period is displayed and the test is repeated. Break by pressing Esc.

ORG H'1510'

WCHR EQU H'0396' writes character in R3

LFCR EQU H'0024' move cursor

KBIN EQU H'030F' read character into R3

HXOT EQU H'006A' hex write byte in R2

INHX EQU H'01B6'

RETU EQU H'0083' return to supervisor

CURS EQU H'17FE'

ESC EQU H'1B'

1510: 3F 00 24 bsta,un LFCR

1513 START:

1513: 0C 15 99 loda,r0 Startp

1516: CC 15 9B stra,r0 MLoc

1519: 20 eorz,r0

151A: CC 15 9C stra,r0 MLoc+1

151D: 07 2E lodi,r3 a'.'

151F: 3F 03 96 bsta,un WCHR

1522 LoopPage:

1522: 0D 15 A3 loda,r1 Cindx

1525: 85 01 addi,r1 1

1527: 45 03 andi,r1 3

1529: CD 15 A3 stra,r1 Cindx

152C: 0D 75 9F loda,r0 CHRS,r1

152F: CC 97 FE stra,r0 *CURS

* Write 5A into the page

* Check that all are 5A

* Repeat using A5, 00, FF

1532: 04 5A lodi,r0 h'5A'

1534: 3B 1B bstr,un TestPage

1536: 04 A5 lodi,r0 h'A5'

1538: 3B 17 bstr,un TestPage

153A: 04 00 lodi,r0 h'00'

153C: 3B 13 bstr,un TestPage

153E: 04 FF lodi,r0 h'FF'

1540: 3B 0F bstr,un TestPage

* Increment Mloc

1542 Inc:

1542: 0C 15 9B loda,r0 Mloc

1545: EC 15 9A coma,r0 Endp

1548: 18 49 bctr,eq START

154A: 84 01 addi,r0 1

154C: CC 15 9B stra,r0 MLoc

154F: 1B 51 bctr,un LoopPage

1551 TestPage:

1551: 05 00 lodi,r1 h'00'

1553 WLoop:

1553: 73 redd,r3

1554: E7 1B comi,r3 ESC

1556: 1C 00 83 bcta,eq RETU

1559: CD F5 9B stra,r0 *Mloc,r1

155C: D9 75 birr,r1 WLoop

* Now compare

155E: C2 strz,r2

;CLoop redd,r3

; comi,r3 ESC

; bcta,eq RETU

155F Cloop:

155F: 0D F5 9B loda,r0 *Mloc,r1

1562: E2 comz,r2

1563: 98 03 bcfr,eq Err

1565: D9 78 birr,r1 Cloop

1567: 17 retc,un

*

1568 Err:

1568: C9 32 strr,r1 Mloc+1

156A: C8 32 strr,r0 Vread

156C: CA 2F strr,r2 Vexp

156E: 0A 2B lodr,r2 Mloc

1570: 3F 00 6A bsta,un HXOT

1573: 0A 27 lodr,r2 Mloc+1

1575: 3F 00 6A bsta,un HXOT

1578: 07 20 lodi,r3 a' '

157A: 3F 03 96 bsta,un WCHR

157D: 0A 1E lodr,r2 Vexp

157F: 3F 00 6A bsta,un HXOT

1582: 07 20 lodi,r3 a' '

1584: 3F 03 96 bsta,un WCHR

1587: 0A 15 lodr,r2 Vread

1589: 3F 00 6A bsta,un HXOT

158C: 07 21 lodi,r3 a'!'

158E: 3F 03 96 bsta,un WCHR

1591: 07 20 lodi,r3 a' '

1593: 3F 03 96 bsta,un WCHR

1596: 1F 15 42 bcta,un Inc

1599 Startp:

1599: 19 data h'19'

159A Endp:

159A: 7F data h'7f'

159B MLoc:

159B: 00 00 ACON 0

159D Vexp:

159D: 00 data 0

159E Vread:

159E: 00 data 0

159F CHRS:

159F: 7C 2F 2D 5C data "|/-\"

15A3 Cindx:

15A3: 00 data 0